Summary

Specifics

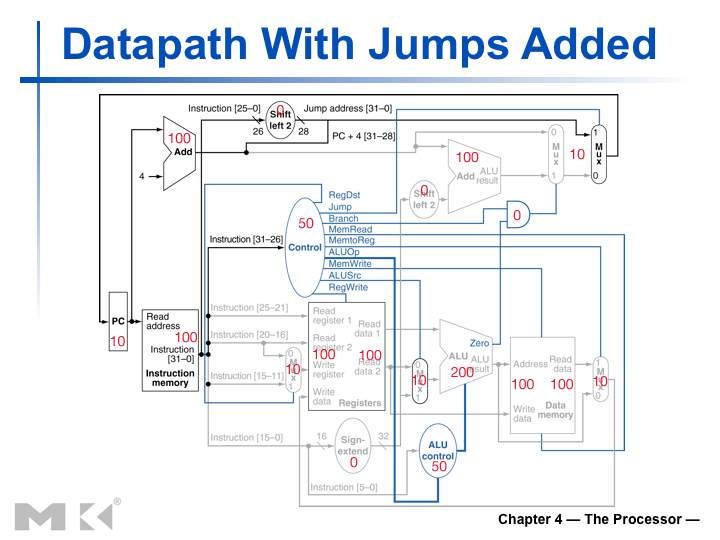

Figure 4.24 on page 329 is a diagram of the complete MIPS single-cycle datapath that you are to analyze. The goal is to determine the maximum clock speed that can be used, given some knowledge about the propagation delays of the various components of the datapath.

Not to give away the answer, but we know that the worst-case number of propagation delays will be for lw instructions because they require the longest sequence of operations to complete (fetch the instruction, read from the register file, compute the effective address, read from data memory, and write back to the register file.) For this assignment, you are to do a detailed analysis to determine just how long this critical path will take. And to be sure we are right about lw being the critical instruction, you are to analyze branch, jump, and R-Type instructions too.

Assumptions

The following table shows the propagation delays we will work with for all the elements in Figure 4.24, in picoseconds.

| Element | picoseconds |

|---|---|

| Multiplexer | 10 |

| Adder | 100 |

| Memory Read | 100 |

| Memory Write | 100 |

| Register file Read | 100 |

| Register file Write | 100 |

| PC read | 10 |

| ALU | 200 |

| Shift | 0 |

| Sign Extend | 0 |

| Control | 50 |

And here is a version of Figure 4.24 with the above values marked in in red:

Notes: Combine the jump and branch multiplexers in the upper right side of Figure 4.24 into one multiplexer, as shown in class. Assume the main control unit and the ALU control each take 50 psec.

Start each analysis with the edge of a clock pulse that loads a new value into the PC.

Write out the answers to all the following questions:

Analysis Procedure: Jump

- How long does it take to fetch the instruction?

- How long does it take the Control Unit to decode the instruction and set the Jump control signal?

- Which takes longer: calculating PC+4 or fetching the instruction from Instruction Memory?

- When is the Jump Address valid?

- When would it be safe for the next clock pulse to occur?

Analysis Procedure: Branch

- How long does it take to fetch the instruction?

- How long does it take the Control Unit to decode the instruction and set the Branch control signal?

- When is the Branch Target Address valid?

- When is the A operand to the ALU valid?

- When is the B operand to the ALU valid?

- When is the function code input to the ALU valid?

- When is the Z output of the ALU valid?

- When would it be safe for the next clock pulse to occur?

Analysis Procedure: R-Type

- How long does it take to fetch the instruction?

- How long does it take the Control Unit to decode the instruction and set the ALUSrc control signal?

- When is the A operand to the ALU valid?

- When is the B operand to the ALU valid?

- When is the function code input to the ALU valid?

- When is the ALU result valid?

- When is the WR Reg input to the register file valid?

- When is the Write Data input to the register file valid?

- When would it be safe for the next clock pulse to occur?

Analysis Procedure: Store

- How long does it take to fetch the instruction?

- How long does it take the Control Unit to decode the instruction and set the ALUSrc control signal?

- When is the A operand to the ALU valid?

- When is the B operand to the ALU valid?

- When is the function code input to the ALU valid?

- When is the ALU result valid?

- When is the MemWrite control signal valid?

- When would it be safe for the next clock pulse to occur?

Analysis Procedure: Load

- How long does it take to fetch the instruction?

- How long does it take the Control Unit to decode the instruction and set the ALUSrc control signal?

- When is the A operand to the ALU valid?

- When is the B operand to the ALU valid?

- When is the function code input to the ALU valid?

- When is the ALU result valid?

- When is the MemRead control signal valid?

- When is the WR Reg input to the register file valid?

- When is the Write Data input to the register file valid?

- When would it be safe for the next clock pulse to occur?

Final Analysis

What is the longest clock period needed for any instruction?

What is the maximum clock frequency that could be used?

Submit The Assignment

Write your answers in the body of an email message (do not send an attachment), and send it to me by midnight of the due date.

Send me email (vickeryatbabbage.cs.qc.cuny.edu) with “CS-343 Assignment 5” as the subject. Be sure to put your name in the body of your message.