# DK4

# **Handel-C Language Reference Manual**

For DK version 4

Celoxica, the Celoxica logo and Handel-C are trademarks of Celoxica Limited.

All other products or services mentioned herein may be trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous development and improvement. All particulars of the product and its use contained in this document are given by Celoxica Limited in good faith. However, all warranties implied or express, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. Celoxica Limited shall not be liable for any loss or damage arising from the use of any information in this document, or any incorrect use of the product.

The information contained herein is subject to change without notice and is for general guidance only.

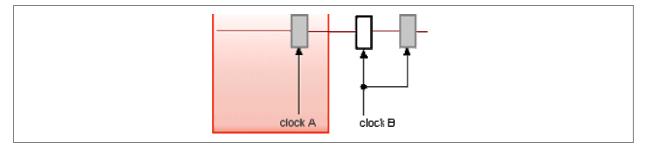

Copyright © 2005 Celoxica Limited. All rights reserved.

Authors: RG

Document number: RM-1003-4.2

Customer Support at http://www.celoxica.com/support/

Celoxica in Europe Celoxica in Japan Celoxica in the Americas

E: sales.emea@celoxica.com E: sales.japan@celoxica.com E: sales.america@celoxica.com

# **Contents**

|     | NTRODUCTION                                     |    |

|-----|-------------------------------------------------|----|

| 2 ( | GETTING STARTED WITH HANDEL-C                   | 12 |

|     | 2.1 Basic concepts                              |    |

|     | 2.1.1 Handel-C programs                         |    |

|     | 2.1.2 Parallel programs                         |    |

|     | 2.1.3 Channel communication                     |    |

|     | 2.1.4 Scope and variable sharing                |    |

| 3 L | _ANGUAGE BASICS                                 | 16 |

|     | 3.1 Program structure                           |    |

|     | 3.2 COMMENTS                                    |    |

|     | 3.3 STATEMENT SUMMARY                           |    |

|     |                                                 |    |

|     | 3.4 OPERATOR SUMMARY                            |    |

|     | 3.5 Type summary                                |    |

| 3   | 3.6 COMPARISON OF HANDEL-C AND ANSI-C           |    |

|     | 3.6.1 Handel-C v C: types and type operators    |    |

|     | 3.6.2 Handel-C v C: floating-point variables    |    |

|     | 3.6.3 Handel-C v C: variable widths and casting |    |

|     | 3.6.4 Handel-C v C: side effects                |    |

|     | 3.6.5 Handel-C v C: functions                   |    |

|     | 3.6.6 Handel-C v C: loop statements             |    |

|     | 3.6.7 Handel-C v C: unions                      |    |

|     | 3.6.9 Handel-C v C: memory allocation           |    |

|     | 3.6.10 Handel-C v C: standard library           |    |

|     | 3.6.11 C and Handel-C types and objects         |    |

|     | 3.6.12 Expressions in C and Handel-C            |    |

|     | 3.6.13 Statements in C and Handel-C             |    |

| 3   | 3.7 HANDEL-C CONSTRUCTS NOT FOUND IN ANSI-C     | 32 |

| 4 E | Declarations                                    | 36 |

| 4   | I.1 Introduction to types                       | 36 |

|     | 4.1.1 Handel-C values and widths                |    |

|     | 4.1.2 String constants                          |    |

|     | 4.1.3 Constants                                 |    |

| 4   | I.2 LOGIC TYPES                                 |    |

|     | 4.2.1 int                                       |    |

|     | 4.2.2 Signed   unsigned syntax                  |    |

|     | 4.2.3 Supported types for porting               |    |

|     | 4.2.4 Inferring widths                          |    |

|     |                                                 |    |

|   | 4.2.5 Arrays                                   |           |

|---|------------------------------------------------|-----------|

|   | 4.2.6 Array indices                            |           |

|   | 4.2.7 struct                                   | 43        |

|   | 4.2.8 enum                                     | 44        |

|   | 4.2.9 Bit fields                               | 45        |

| 4 | .3 POINTERS                                    | 46        |

|   | 4.3.1 Pointers and addresses                   | 48        |

|   | 4.3.2 Pointers to functions                    | 48        |

|   | 4.3.3 Pointers to interfaces                   | 49        |

|   | 4.3.4 Structure pointers                       |           |

|   | 4.3.5 address and indirection operators        |           |

| 4 | .4 Architectural types                         |           |

|   | .5 CHANNELS                                    |           |

| _ | 4.5.1 FIFO code example                        |           |

|   | 4.5.2 Arrays of channels                       |           |

|   | 4.5.3 Restrictions on channel accesses         |           |

|   | 4.5.4 Timing and latency in FIFOs              |           |

| 4 | •                                              |           |

| 4 | .6 INTERFACES: OVERVIEW                        |           |

|   | 4.6.1 Interface declaration                    |           |

|   | 4.6.2 Interface definition                     |           |

|   | 4.6.3 Example interface to external code       |           |

| _ | 4.6.4 Interface specifications                 |           |

| 4 | .7 RAMs and ROMs                               |           |

|   | 4.7.1 Initialization                           |           |

|   | 4.7.2 Inferring size from use                  |           |

|   | 4.7.3 Accessing RAMs and ROMs                  |           |

|   | 4.7.4 Differences between RAMs and arrays      |           |

|   | 4.7.5 RAM and ROM support on different devices |           |

|   | 4.7.6 Multidimensional memory arrays           |           |

| 4 | .8 MPRAM (MULTI-PORTED RAMS)                   |           |

|   | 4.8.1 Initialization of mprams                 |           |

|   | 4.8.2 Mapping of different width mpram ports   |           |

|   | 4.8.3 mprams example                           | 68        |

| 4 | .9 WOM (WRITE-ONLY MEMORY)                     | 69        |

| 4 | .10 SEMA                                       | 69        |

|   | .11 SIGNAL                                     |           |

|   | .12 STORAGE CLASS SPECIFIERS                   |           |

| 4 | 4.12.1 auto                                    |           |

|   | 4.12.1 auto                                    |           |

|   | ·                                              |           |

|   | .13 EXTERN LANGUAGE CONSTRUCT                  |           |

| 4 | .14 REGISTER                                   | <b>75</b> |

| 4 | .15 INLINE FUNCTIONS                           | <b>75</b> |

| 4 | .16 STATIC                                     | 76        |

|   | .17 TYPEDEF                                    |           |

|   | .18 TYPEOF                                     |           |

|   |                                                |           |

| 4 | .19 CONST                                      | 78        |

| 4.20 VOLATILE                                                  | 78  |

|----------------------------------------------------------------|-----|

| 4.21 COMPLEX DECLARATIONS                                      |     |

| 4.21.1 Macro expressions in widths                             |     |

| 4.21.2 <> (type clarifier)                                     |     |

| 4.21.3 Using signals to split up complex expressions           |     |

| 4.22 VARIABLE INITIALIZATION                                   |     |

| T.22 VARIABLE INTITALIZATION                                   |     |

| 5 Statements                                                   | 82  |

| 5.1 SEQUENTIAL AND PARALLEL EXECUTION                          | 82  |

| 5.2 SEQ 83                                                     |     |

|                                                                | 0.2 |

| 5.3 REPLICATED PAR AND SEQ                                     |     |

| 5.4 PRIALT                                                     |     |

| 5.5 Using prialt: examples                                     |     |

| 5.6 Assignments                                                | 88  |

| 5.6.1 continue                                                 |     |

| 5.6.2 goto                                                     |     |

| 5.6.3 return [expression]                                      |     |

| 5.6.4 Conditional execution (if else)                          |     |

| 5.6.5 while loops                                              |     |

| 5.6.6 do while loops                                           |     |

| 5.6.7 for loops                                                |     |

| 5.6.8 switch                                                   |     |

| 5.6.9 break                                                    |     |

| 5.6.10 delay<br>5.6.11 try reset                               |     |

| 5.6.12 trysema()                                               |     |

| 5.6.13 releasesema()                                           |     |

| 3.0.13 releasesema()                                           |     |

| 6 Expressions                                                  | 102 |

| 6.1 Introduction to expressions                                |     |

| 6.1.1 Clock cycles required                                    |     |

| 6.1.2 Breaking down complex expressions                        |     |

| 6.1.3 Prefix and postfix operators                             |     |

| 6.2 CASTING OF EXPRESSION TYPES                                |     |

| 6.2.1 Restrictions on casting                                  |     |

| 6.3 RESTRICTIONS ON RAMS AND ROMS                              |     |

| 6.4 ASSERT                                                     |     |

|                                                                |     |

| 6.5 BIT MANIPULATION OPERATORS                                 |     |

| 6.5.1 Shift operators                                          |     |

| 6.5.2 Take / drop operators                                    |     |

| 6.5.3 Concatenation operator                                   |     |

| 6.5.5 Width operator                                           |     |

| 6.6 ARITHMETIC OPERATORS                                       |     |

|                                                                |     |

| <b>6.7 RELATIONAL OPERATORS</b> 6.7 1 Signed/unsigned compares |     |

| o / L.MODEO/ODNOHEO COMDALES                                   |     |

| 6.7.2 Implicit compares                                                          | 114 |

|----------------------------------------------------------------------------------|-----|

| 6.8 LOGICAL OPERATORS                                                            | 114 |

| 6.8.1 Bitwise logical operators                                                  | 115 |

| 6.9 CONDITIONAL OPERATOR                                                         | 116 |

| 6.10 Member operators (. / ->)                                                   | 116 |

| 7.5                                                                              | 110 |

| 7 FUNCTIONS AND MACROS                                                           |     |

| 7.1 FUNCTIONS AND MACROS: OVERVIEW                                               |     |

| 7.1.1 Functions and macros: language issues                                      |     |

| 7.1.2 Functions and macros: sharing hardware                                     |     |

| 7.1.3 Functions and macros: clock cycles                                         |     |

| 7.1.4 Functions and macros: examples                                             |     |

| 7.1.6 Recursion in macros and functions                                          |     |

|                                                                                  |     |

| <b>7.2 INTRODUCTION TO FUNCTIONS</b> 7.2.1 Function definitions and declarations |     |

| 7.2.2 Functions: scope                                                           |     |

| 7.2.3 Arrays of functions                                                        |     |

| 7.2.4 Function arrays: example                                                   |     |

| 7.2.5 Function arrays example with static variables                              |     |

| 7.2.6 Function pointers                                                          |     |

| 7.2.7 Function pointers example                                                  |     |

| 7.2.8 Simultaneous function calls                                                |     |

| 7.2.9 Multiple functions in a statement                                          |     |

| 7.3 Introduction to macros                                                       |     |

| 7.3.1 Non-parameterized macro expressions                                        |     |

| 7.3.2 Parameterized macro expressions                                            |     |

| 7.3.3 select operator                                                            |     |

| 7.3.4 ifselect                                                                   |     |

| 7.3.5 Recursive macro expressions                                                |     |

| 7.3.6 Recursive macro expressions example                                        |     |

| 7.3.7 Shared expressions                                                         |     |

| 7.3.8 Using recursion to generate shared expressions                             |     |

| 7.3.9 Restrictions on shared expressions                                         |     |

| 7.3.10 let in                                                                    |     |

| 7.3.11 Macro procedures                                                          |     |

| 7.3.12 Macro procedures compared to pre-processor macros                         | 146 |

| 8 Introduction to timing                                                         | 148 |

| 8.1 STATEMENT TIMING                                                             | 148 |

| 8.1.1 Example timings                                                            | 148 |

| 8.1.2 Statement timing summary                                                   |     |

| 8.2 AVOIDING COMBINATIONAL LOOPS                                                 | 156 |

| 8.3 Parallel access to variables                                                 | 158 |

| 8.4 DETAILED TIMING EXAMPLE                                                      | 159 |

| 8.5 TIME EFFICIENCY OF HANDEL-C HARDWARE                                         | 161 |

| 8.5.1 Reducing logic depth                                                       | 161 |

| 8.5.2 Pipelining                                                          | 164 |

|---------------------------------------------------------------------------|-----|

| 9 CLOCKS OVERVIEW                                                         | 167 |

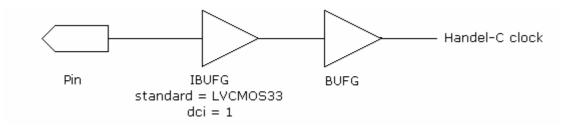

| 9.1 LOCATING THE CLOCK                                                    | 167 |

| 9.1.1 External clocks                                                     | 168 |

| 9.1.2 Internal clocks fed from expressions                                | 168 |

| 9.2 CURRENT CLOCK                                                         | 169 |

| 9.3 Multiple clock domains                                                | 169 |

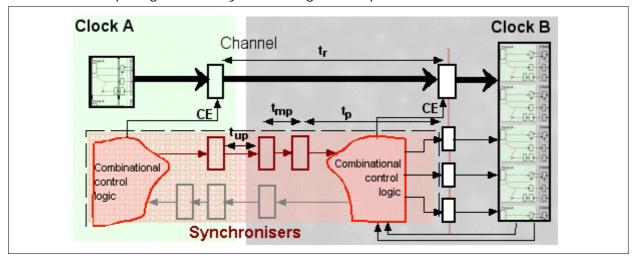

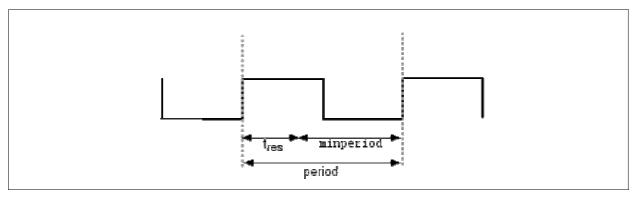

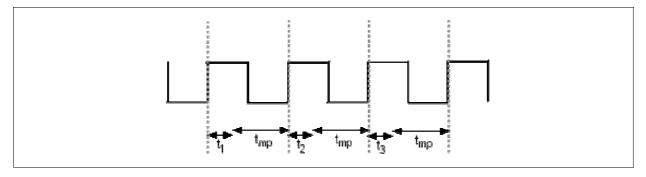

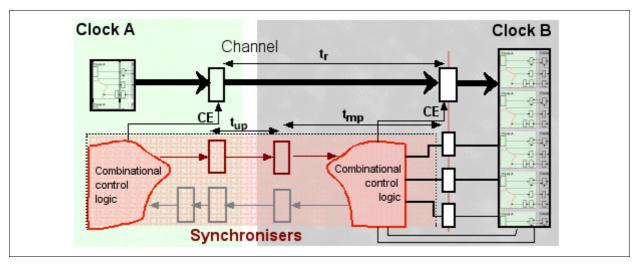

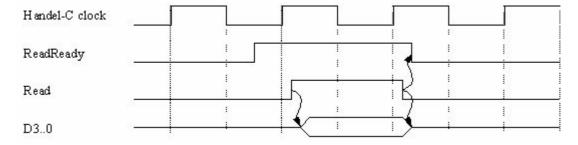

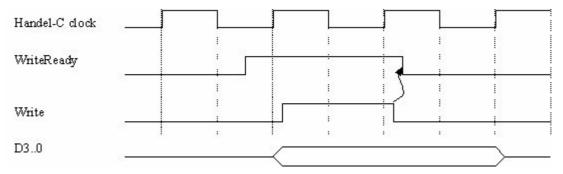

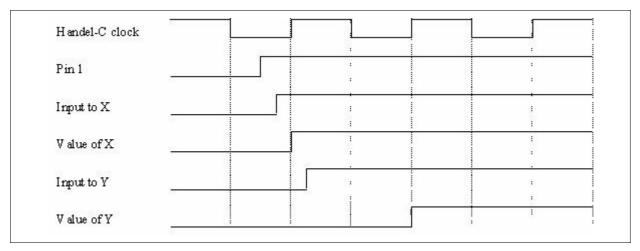

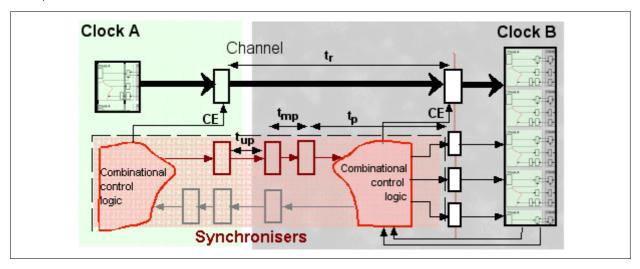

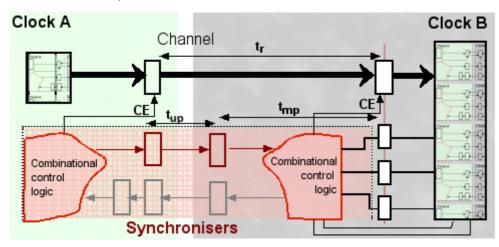

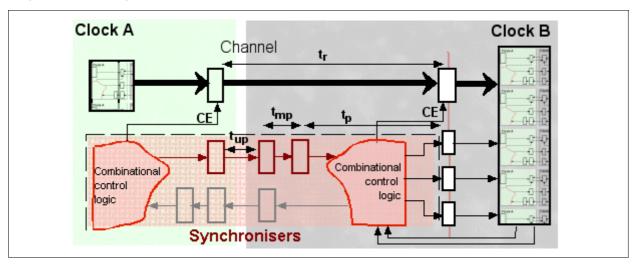

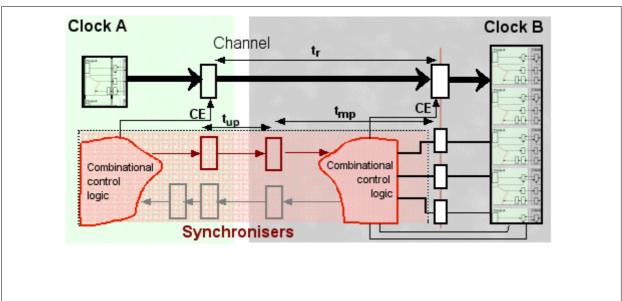

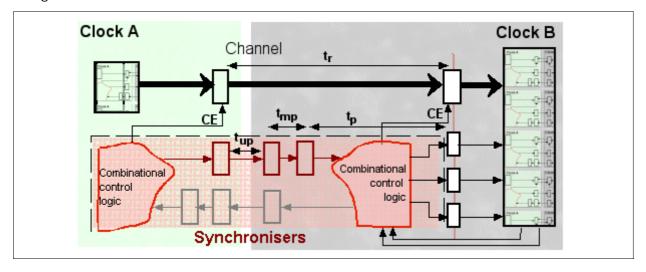

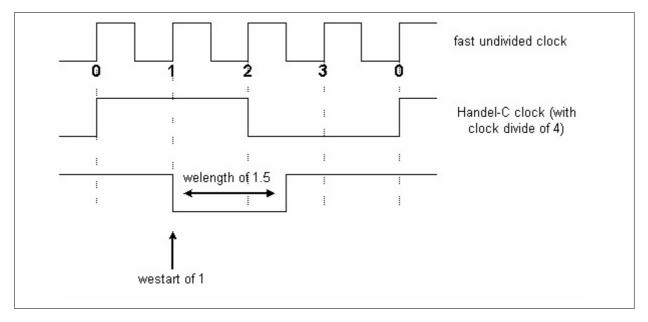

| 9.3.1 Channels communicating between clock domains                        |     |

| 9.3.2 Simulating multiple clock domains                                   |     |

| 10 Targeting hardware and simulation                                      | 184 |

| 10.1 Interfacing with the simulator                                       | 184 |

| 10.1.1 Simulator input file format                                        | 185 |

| 10.1.2 Block data transfers                                               | 185 |

| 10.2 Targeting FPGA and PLD devices                                       | 186 |

| 10.2.1 Summary of supported devices                                       | 187 |

| 10.2.2 Detecting the current device family                                | 189 |

| 10.2.3 Targeting specific devices via source code                         | 190 |

| 10.2.4 Specifying a global reset                                          |     |

| 10.3 Use of RAMs and ROMs with Handel-C                                   | 193 |

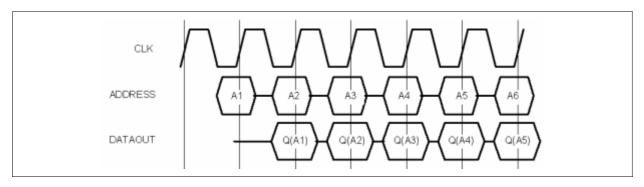

| 10.3.1 Asynchronous RAMs                                                  |     |

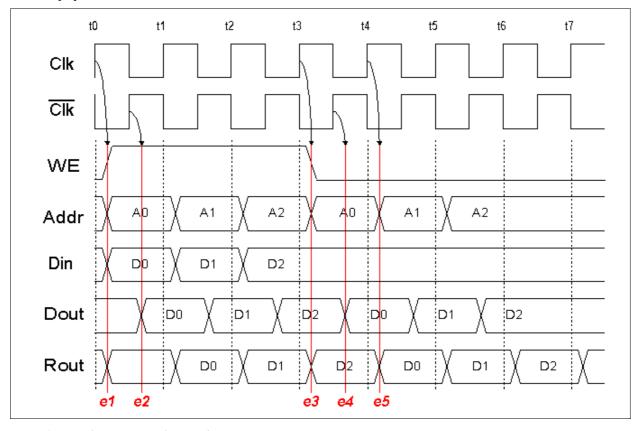

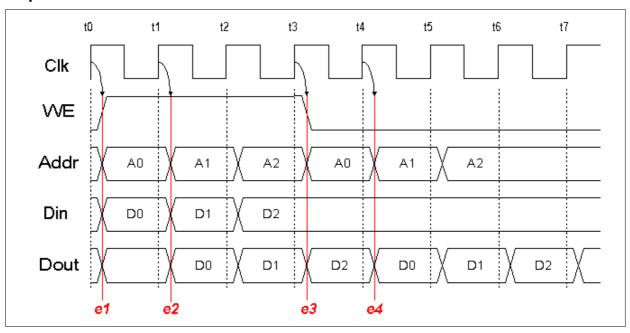

| 10.3.2 Synchronous RAMs                                                   | 200 |

| 10.3.3 Targeting Stratix and Cyclone memory blocks                        |     |

| 10.3.4 Using on-chip RAMs in Actel devices                                |     |

| 10.3.5 Using on-chip RAMs in Altera devices                               |     |

| 10.3.6 Using on-chip RAMs in Xilinx devices                               |     |

| 10.3.7 Using external ROMs                                                |     |

| 10.3.8 Connecting to RAMs in foreign code                                 |     |

| 10.3.9 Using other RAMs                                                   | 224 |

| 11 INTERFACING WITH EXTERNAL HARDWARE                                     | _   |

| 11.1 INTERFACE SORTS                                                      |     |

| 11.1.1 Reading from external pins bus_in                                  |     |

| 11.1.2 Registered reading from external pins: bus_latch_in                |     |

| 11.1.3 Clocked reading from external pins: bus_clock_in                   |     |

| 11.1.4 Writing to external pins: bus_out                                  |     |

| 11.1.6 Bidirectional data transfer with registered input: bus_ts_latch_in |     |

| 11.1.7 Bidirectional data transfer with clocked input: bus_ts_clock_in    |     |

| 11.1.8 Example hardware interface                                         |     |

| 11.2 SIMULATING INTERFACES                                                |     |

| 11.3 BUSES AND THE SIMULATOR                                              |     |

|                                                                           |     |

| 11.4 Merging clock pins                                                   |     |

| 11.4.1 Merging clock pins                                                 |     |

| 11.4.3 Merging tri-state pins                                             |     |

| The morging the state pins                                                | 237 |

| 11.5 TIMING CONSIDERATIONS FOR BUSES                      | 240 |

|-----------------------------------------------------------|-----|

| 11.5.1 Example timing considerations for input buses      |     |

| 11.5.2 Example timing considerations for output buses     |     |

| 11.6 Metastability                                        | 242 |

| 11.6.1 Techniques to minimize the problem                 |     |

| 11.6.2 Using interfaces: External resynchronizing example |     |

| 11.7 PORTS: INTERFACING WITH EXTERNAL LOGIC               |     |

| 11.8 SPECIFYING THE INTERFACE                             |     |

| 11.9 TARGETING PORTS TO SPECIFIC TOOLS                    | 250 |

| 12 Object specifications                                  | 252 |

| 12.1 SUMMARY OF SPECIFICATIONS                            |     |

| 12.1.1 Compiler atttributes                               |     |

| 12.1.2 Simulator attributes                               |     |

| 12.1.3 Clock attributes                                   | 254 |

| 12.1.4 Channel attributes                                 |     |

| 12.1.5 Channel and memory attributes                      |     |

| 12.1.6 Memory attributes                                  |     |

| 12.1.8 Interface and memory attributes                    |     |

| 12.1.9 Examples                                           |     |

| 12.2 BASE SPECIFICATION                                   |     |

| 12.3 BIND SPECIFICATION                                   |     |

| 12.4 BLOCK SPECIFICATION                                  |     |

| 12.5 BUFFER SPECIFICATION                                 |     |

| 12.6 BUSFORMAT SPECIFICATION                              |     |

| 12.7 SPECIFYING THE CLOCK PIN FOR SSRAM                   |     |

| 12.8 CLOCKPORT SPECIFICATION                              |     |

| 12.9 DATA SPECIFICATION (PIN CONSTRAINTS)                 |     |

| 12.10 DCI SPECIFICATION                                   |     |

| 12.11 EXTINST, EXTLIB, EXTFUNC SPECIFICATIONS             |     |

| 12.12 EXTPATH SPECIFICATION                               |     |

| 12.13 FIFOLENGTH SPECIFICATION                            |     |

| 12.14 INFILE AND OUTFILE SPECIFICATIONS                   |     |

| 12.15 INTIME AND OUTTIME SPECIFICATIONS                   | 276 |

| 12.16 TIMING CONSTRAINTS EXAMPLE                          | 277 |

| 12.17 MINPERIOD SPECIFICATION                             | 280 |

| 12.18 OFFCHIP SPECIFICATION                               | 281 |

| 12.19 PARANOIA SPECIFICATION                              | 282 |

| 12.20 PIN SPECIFICATIONS                                  | 283 |

| 12.21 PORTS SPECIFICATION                                 |     |

| 12.22 PROPERTIES SPECIFICATION                            |     |

| 12.23 PULL SPECIFICATION                                  |     |

| 12.24 QUARTUS_PROJ_ASSIGN SPECIFICATION                      | 288 |

|--------------------------------------------------------------|-----|

| 12.25 RATE SPECIFICATION                                     |     |

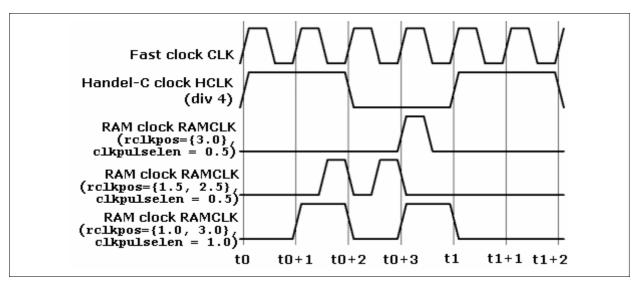

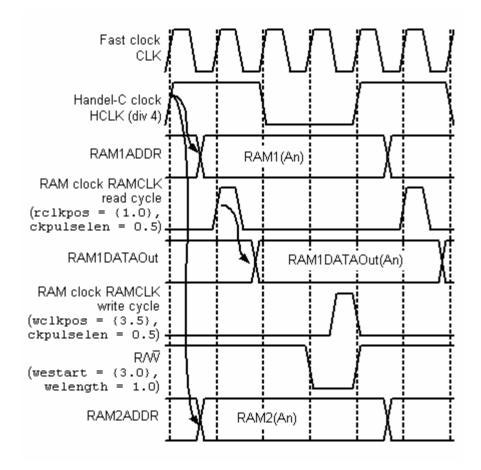

| 12.26 RCLKPOS, WCLKPOS AND CLKPULSELEN SPECIFICATIONS (SSRAM |     |

| TIMING)                                                      | 289 |

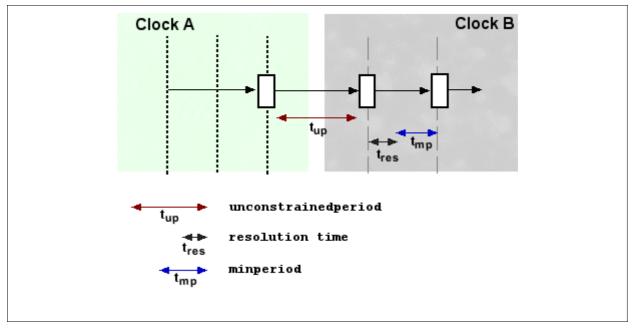

| 12.27 RESOLUTIONTIME SPECIFICATION                           | 291 |

| 12.28 RETIME SPECIFICATION                                   | 291 |

| 12.29 SC_TYPE SPECIFICATION                                  | 292 |

| 12.30 SHOW SPECIFICATION                                     | 293 |

| 12.31 SPEED SPECIFICATION                                    | 293 |

| 12.32 STANDARD SPECIFICATION                                 |     |

| 12.32.1 Available I/O standards                              |     |

| 12.32.2 I/O standards supported by different chips           |     |

| 12.32.4 Differential I/O standards                           |     |

| 12.33 STD_LOGIC_VECTOR SPECIFICATION                         |     |

| 12.34 STRENGTH SPECIFICATION                                 |     |

| 12.35 SYNCHRONOUS SPECIFICATION                              |     |

| 12.36 UNCONSTRAINEDPERIOD SPECIFICATION                      |     |

| 12.37 VHDL_TYPE SPECIFICATION                                |     |

| 12.38 WARN SPECIFICATION                                     |     |

| 12.39 WEGATE SPECIFICATION                                   |     |

| 12.40 WESTART AND WELENGTH SPECIFICATIONS                    | 307 |

|                                                              |     |

| 13 Handel-C preprocessor                                     |     |

| 13.1 Preprocessor macros                                     |     |

| 13.2 FILE INCLUSION                                          |     |

| 13.3 CONDITIONAL COMPILATION                                 |     |

| 13.4 LINE CONTROL                                            |     |

| 13.5 CONCATENATION IN MACROS                                 |     |

| 13.6 ERROR GENERATION                                        |     |

| 13.7 PREDEFINED MACRO SUBSTITUTION                           |     |

| 13.8 LINE SPLICING                                           | 314 |

| 14 Language syntax                                           | 316 |

| 14.1 LANGUAGE SYNTAX CONVENTIONS                             |     |

| 14.2 KEYWORD SUMMARY                                         |     |

| 14.3 CONSTANT EXPRESSIONS                                    |     |

| 14.3.1 Identifiers: syntax                                   |     |

| 14.3.2 Integer constants: syntax                             | 322 |

| 14.3.3 Character constants: syntax                           |     |

| 14.3.4 Strings: syntax                                       |     |

| 14.3.5 Floating-point constants: syntax                      |     |

| 14.4 FUNCTIONS AND DECLARATIONS: SYNTAX                      | ა∠ა |

| 14.5 Macro/shared exprs/procs: syntax             | 324 |

|---------------------------------------------------|-----|

| 14.6 Interfaces: syntax                           |     |

| 14.7 STRUCTURES AND UNIONS: SYNTAX                |     |

| 14.8 ENUMERATED TYPES: SYNTAX                     |     |

| 14.9 SIGNAL SPECIFIERS: SYNTAX                    |     |

| 14.10 Channel Syntax                              |     |

| 14.11 RAM SPECIFIERS: SYNTAX                      |     |

| 14.12 DECLARATORS: SYNTAX                         |     |

| 14.13 FUNCTION PARAMETERS: SYNTAX                 |     |

| 14.14 Type names and abstract declarators: syntax |     |

| 14.15 STATEMENTS: SYNTAX                          |     |

| 14.15.1 Compound statements with replicators      |     |

| 14.16 REPLICATORS: SYNTAX                         |     |

| 14.17 EXPRESSIONS: SYNTAX                         |     |

| 15 INDEX                                          | 225 |

# **Conventions**

A number of conventions are used in this document. These conventions are detailed below.

Warning Message. These messages warn you that actions may damage your hardware.

Handy Note. These messages draw your attention to crucial pieces of information.

Hexadecimal numbers will appear throughout this document. The convention used is that of prefixing the number with '0x' in common with standard C syntax.

Sections of code or commands that you must type are given in typewriter font like this: void main();

Information about a type of object you must specify is given in italics like this: copy SourceFileName DestinationFileName

Optional elements are enclosed in square brackets like this:

struct [type\_Name]

Curly brackets around an element show that it is optional but it may be repeated any number of times.

string ::= "{character}"

# **Assumptions & Omissions**

This manual assumes that you:

- have used Handel-C or have the Handel-C Language Reference Manual

- are familiar with common programming terms (e.g. functions)

- are familiar with MS Windows

This manual does not include:

- instruction in VHDL or Verilog

- instruction in the use of place and route tools

- tutorial example programs. These are provided in the Handel-C User Manual

# 1 Introduction

## 1.1 References

The C Programming Language 2nd Edition Kernighan, B. and Ritchie, D. Prentice-Hall, 1988

Altera Databook Altera 2004 www.altera.com/literature/lit-index.html

Xilinx Data Book Xilinx 2004 www.xilinx.com/literature/index.htm

• VHDL for logic synthesis Author: Andrew Rushton Publisher: John Wiley and Sons ISBN: 0-471-98325-X

Published: May 1998

IEEE standard 1364 -1995 IEEE Standard Hardware Description Language Based on the Verilog® Hardware Description Language. http://standards.ieee.org/

# 2 Getting started with Handel-C

## 2.1 Basic concepts

Handel-C uses much of the syntax of conventional C with the addition of inherent parallelism. You can write sequential programs in Handel-C, but to gain maximum benefit in performance from the target hardware you must use its parallel constructs. These may be new to some users. If you are familiar with conventional C you will recognize nearly all the other features.

Handel-C programs

- · Parallel programs

- Channel communications

- Scope and variable sharing

## 2.1.1 Handel-C programs

Since Handel-C is based on the syntax of conventional C, programs written in Handel-C are implicitly sequential. Writing one command after another indicates that those instructions should be executed in that exact order. To execute instructions in parallel, you must use the par keyword.

Handel-C provides constructs to control the flow of a program. For example, code can be executed conditionally depending on the value of some expression, or a block of code can be repeated a number of times using a loop construct.

You can express your algorithm in Handel-C without worrying about how the underlying computation engine works. This philosophy makes Handel-C a programming language rather than a hardware description language. In some senses, Handel-C is to hardware what a conventional high-level language is to microprocessor assembly language.

The hardware design that DK produces is generated directly from the Handel-C source program. There is no intermediate 'interpreting' layer as exists in assembly language when targeting general-purpose microprocessors. The logic gates that make up the final Handel-C circuit are the assembly instructions of the Handel-C system.

## 2.1.2 Parallel programs

The target of the Handel-C compiler is low-level hardware. This means that you get massive performance benefits by using parallelism. It is essential for writing efficient programs to instruct the compiler to build hardware to execute statements in parallel. Handel-C parallelism is true parallelism, not the time-sliced parallelism familiar from general-purpose computers. When instructed to execute two instructions in parallel,

those two instructions will be executed at exactly the same instant in time by two separate pieces of hardware.

When a parallel block is encountered, execution flow splits at the start of the parallel block and each branch of the block executes simultaneously. Execution flow then re-joins at the end of the block when all branches have completed. Any branches that complete early are forced to wait for the slowest branch before continuing.

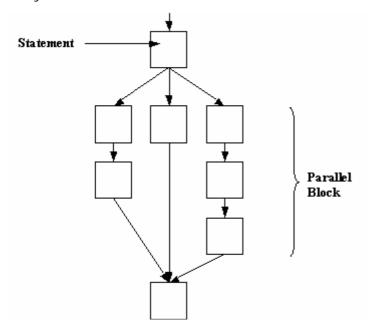

This diagram illustrates the branching and re-joining of the execution flow. The left hand and middle branches must wait to ensure that all branches have completed before the instruction following the parallel construct can be executed.

#### 2.1.3 Channel communication

Channels provide a link between branches executing in parallel. One parallel branch outputs data onto the channel and the other branch reads data from the channel.

Channels can be constructed with and without FIFO capacities

- Channels constructed as FIFOs

- A channel can be constructed as a FIFO queue. In this case, the data is written to the head of the FIFO and is read from the tail. If the FIFO is full, a write blocks until an element is read from the FIFO. If the FIFO is empty, a read blocks until there is data ready to be read.

- Channels constructed without FIFO capacity

These channels provide synchronization between parallel branches because the data transfer can only complete when both the transmitter and the receiver are ready. If one side is not ready, the other must wait.

## Channel synchronization

#### SYNCHRONIZATION OF NORMAL CHANNELS

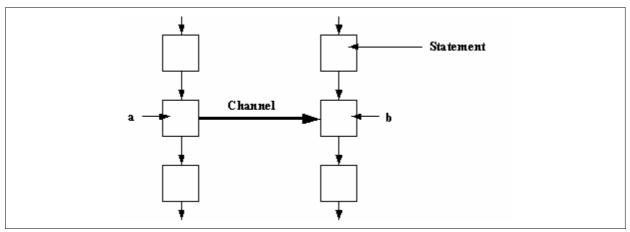

Here, the channel is shown transferring data from the left branch to the right branch. If the left branch reaches point a before the right branch reaches point b, the left branch waits at point a until the right branch reaches point b.

## Communication without synchronization

If you are using a channel FIFO, the left branch will not have to wait at point a if there is space in the FIFO. Instead, it can write to the FIFO once per clock tick until the FIFO is full. Only then will it have to wait. Each time the right branch reads from the FIFO at point b, the data at the head of the FIFO is read, and the next piece of data becomes the head. The right branch must wait if the FIFO is empty.

In this case, the two branches will not be synchronized after every read and write.

## 2.1.4 Scope and variable sharing

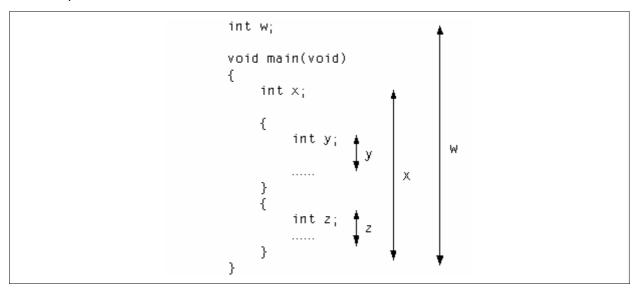

The scope of declarations is based around code blocks. A code block is denoted with  $\{...\}$  brackets. This means that:

- Global variables must be declared outside all code blocks

- An identifier is in scope within a code block and any sub-blocks of that block.

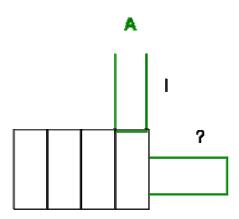

The scope of variables is illustrated below:

Since parallel constructs are simply code blocks, variables can be in scope in two parallel branches of code. This can lead to resource conflicts if the variable is written to simultaneously by more than one of the branches. Handel-C states that a single variable must not be written to by more than one parallel branch but may be read from by several parallel branches.

If you wish to write to the same variable from several processes, the correct way to do so is by using channels which are read from in a single process. This process can use a prialt statement to select which channel is ready to be read from first, and that channel is the only one which will be allowed to write to the variable.

```

while(1)

prialt

{

case chan1 ? y:

break;

case chan2 ? y:

break;

case chan3 ? y:

break;

}

```

In this case, three separate processes can attempt to change the value of y by sending data down the channels, chan1, chan2 and chan3. y will be changed by whichever process sends the data first.

A single variable should not be written to by more than one parallel branch.

# 3 Language basics

## 3.1 Program structure

## Sequential structure

As in a conventional C program, a Handel-C program consists of a series of statements which execute sequentially. These statements are contained within a main() function that tells the compiler where the program begins. The body of the main function may be split into a number of blocks using {...} brackets to break the program into readable chunks and restrict the scope of variables and identifiers.

Handel-C also has functions, variables and expressions similar to conventional C. There are restrictions where operations are not appropriate to hardware implementation and extensions where hardware implementation allows additional functionality.

#### Parallel structure

Unlike conventional C, Handel-C programs can also have statements or functions that execute in parallel. This feature is crucial when targeting hardware because parallelism is the main way to increase performance by using hardware. Parallel processes can communicate using channels. A channel is a point-to-point link between two processes.

#### **Overall structure**

The overall program structure consists of one or more main functions, each associated with a clock. This is unlike conventional C, where only one main function is permitted. You would only use more than one main function if you needed parts of your program to run at different speeds (and so use different clocks). A main function is defined as follows:

```

Global Declarations

Clock Definition

void main(void)

{

Local Declarations

Body Code

}

```

The main() function takes no arguments and returns no value. This is in line with a hardware implementation where there are no command line arguments and no environment to return values to. The argc, argv and envp parameters and the return value familiar from conventional C can be replaced with explicit communications with an external system (e.g. a host microprocessor) within the body of the program.

## 3.2 Comments

Handel-C uses the standard  $/* \dots */$  delimiters for comments. These comments may not be nested. For example:

```

/* Valid comment */

/* This is /* NOT */ valid */

```

Handel-C also provides the C++ style // comment marker which tells the compiler to ignore everything up to the next new line. For example

```

x = x + 1; // This is a comment

```

## 3.3 Statement summary

| Statement                                                     | Meaning                             |

|---------------------------------------------------------------|-------------------------------------|

| par {}                                                        | Parallel execution                  |

| seq {}                                                        | Sequential execution                |

| par ( <i>Init</i> ; <i>Test</i> ; <i>Iter</i> ){}             | Parallel replication                |

| <pre>seq (Init ; Test ; Iter){}</pre>                         | Sequential replication              |

| Variable = <i>Expression</i> ;                                | Assignment                          |

| Variable ++;                                                  | Increment                           |

| Variable;                                                     | Decrement                           |

| ++ Variable;                                                  | Increment                           |

| Variable;                                                     | Decrement                           |

| <pre>Variable += Expression;</pre>                            | Add and assign                      |

| <i>Variable -= Expression</i> ;                               | Subtract and assign                 |

| <i>Variable</i> *= <i>Expression</i> ;                        | Multiply and assign                 |

| Variable /= Expression;                                       | Divide and assign                   |

| Variable %= Expression;                                       | Modulo and assign                   |

| <pre>Variable &lt;&lt;= Expression;</pre>                     | Shift left and assign               |

| <pre>Variable &gt;&gt;= Expression;</pre>                     | Shift right and assign              |

| Variable &= Expression;                                       | Bitwise AND and assign              |

| <i>Variable</i>  = <i>Expression</i> ;                        | Bitwise OR and assign               |

| Variable ^= Expression;                                       | Bitwise XOR and assign              |

| Channel ? Variable;                                           | Channel input                       |

| Channel ! Expression;                                         | Channel output                      |

| <pre>if (Expression) {statement} [else {statement}]</pre>     | Conditional execution               |

| <pre>ifselect (Expression) {statement}</pre>                  | Conditional compilation             |

| <pre>[else {statement}]</pre>                                 |                                     |

| while ( <i>Expression</i> ) { statement}                      | Iteration                           |

| <pre>do {} while (Expression);</pre>                          | Iteration                           |

| for ( $Init$ ; $Test$ ; $Iter$ ) {}                           | Iteration                           |

| break;                                                        | Loop, switch and prialt termination |

| continue;                                                     | Resume execution                    |

| <pre>return[([Expression])];</pre>                            | Return from function                |

| goto <i>label</i> ;                                           | Jump to label                       |

| $\verb switch  (\textit{Expression}) \{\textit{statement}\} $ | Selection                           |

| <pre>prialt {statement}</pre>                                 | Channel alternation                 |

releasesema() Make semaphore available after use of

trysema expression

try{...} Perform statements on reset condition

reset(Condition){statement}

delay; Single cycle delay

Note: RAM and ROM elements, signals and array elements are included in the set of variables above. However,

ram x [3];

x[0]++;

is invalid.

The assignment group of operations and the increment and decrement operations are included as statements to reflect the fact that Handel-C expressions cannot contain side effects.

# 3.4 Operator summary

The following table lists all operators. Entries at the top have the highest precedence and entries at the bottom have the lowest precedence. Entries within the same group have the same precedence. Precedence of operators is as expected from conventional C. For example:

```

x = x + y * z;

```

This performs the multiplication before the addition. Brackets may be used to ensure the correct calculation order as in conventional C.

Note that assignments are not true operators in Handel-C.

| Operator | Meaning |

|----------|---------|

trysema Test if semaphore owned. Take if not

select(Constant, Expr, Expr) Compile-time selection

Expression [Expression] Array or memory subscripting

Expression [Constant ]

Bit selection

Expression [Constant: Bit range extraction. One of the two constants may

Constant] be omitted (but not both).

functionName (Arguments ) Function call

! Expression Logical NOT

~ Expression Bitwise NOT

- Expression Unary minus

+ Expression Unary plus

& object Yields pointer to operand

\* pointer Yields object or function that the operand points to

width(Expression) Width of expression

Expression / Expression Division

Expression % Expression Modulo arithmetic

Expression + ExpressionAdditionExpression - ExpressionSubtractionExpression << ExpressionShift leftExpression >> ExpressionShift rightExpression @ ExpressionConcatenation

Expression < Expression Less than Expression > Expression Greater than

$Expression \leftarrow Expression$  Less than or equal  $Expression \rightarrow Expression$  Greater than or equal

Expression == Expression Equal Expression != Expression Not equal Expression & Expression Bitwise AND  $Expression \land Expression$  Bitwise XOR

ExpressionExpressionBitwise ORExpression && ExpressionLogical ANDExpression || ExpressionLogical OR

Expression ? Expr : Expr Conditional selection

assert diagnostic macro to print to stderr

## 3.5 Type summary

The most common types that may be associated with a variable, and the prefixes for architectural and compound types are listed below.

## **Common logic types**

| Туре                                         | Width                 |

|----------------------------------------------|-----------------------|

| int                                          | See *Note 1           |

| [signed   unsigned] int n                    | n bits                |

| <pre>[signed   unsigned] int undefined</pre> | Compiler infers width |

| [signed   unsigned] char                     | 8 bits                |

| [signed   unsigned] short                    | 16 bits               |

| [signed   unsigned] long                     | 32 bits               |

| [signed   unsigned] int32                    | 32 bits               |

| [signed   unsigned] int64                    | 64 bits               |

| typeof ( <i>Expression</i> )                 | Yields type of object |

<sup>\*</sup>Note 1: Width will be inferred by compiler unless the 'set intwidth = n' command appears before the declaration.

### **Architectural types**

Prefixes to the above types for different architectural object types are:

Prefix Object

chan Channel

chanin Simulator channel chanout Simulator channel

ram Internal or external RAM rom Internal or external ROM

signal Wire

wom WOM within multi-port memory

#### **Compound types**

The compound types are:

Prefix Object

struct Structure

mpram Multi-port memory

## Special types

Type Object

interface Interface to external logic or devicesemaSemaphore. Has no width or logic type

Interfaces connect to logic beyond the Handel-C design, whether on the same or a different device.

## 3.6 Comparison of Handel-C and ANSI-C

Handel-C has many similarities to ANSI-C (ISO-C). However, Handel-C is a language for digital logic design, which means that the way in which DK interprets it may different to the way in which compilers interpret ANSI-C for software design. Handel-C has some extensions to ANSI-C, to allow additional functionality for hardware design. It also lacks some ANSI-C constructs which are not appropriate to hardware implementation.

This section summarizes the differences between Handel-C and ANSI-C. It is not a definitive list. Refer to specific sections to see how DK implements each of the language constructs.

## 3.6.1 Handel-C v C: types and type operators

Handel-C supports all ANSI-C types apart from float, double and long double. You can still perform floating-point arithmetic.

char, short and long are supported to help the porting of code from ANSI-C. However, it can be better (more efficient in hardware terms) to re-express these as a signed or unsigned int of a specific width. In Handel-C, ints are not limited to 64 bits.

Handel-C has a range of additional types for creating channels and interfaces between different hardware blocks, and for specifying memories and signals. The Celoxica wide number library provides signed and unsigned compiler-independent implementations of int32 and int64.

Handel-C also allows all ANSI-C storage class specifiers and type qualifiers, but volatile and register have no meaning in hardware terms, and are accepted for compatibility only.

You have to specify the size of an array in Handel-C. For example, you couldn't write:

```

int ai[SIZE]

```

and then # define SIZE.

Handel-C variables can only be initialized if they are static, const or global. Otherwise, you must assign a value to them in a statement.

```

int a = 8 //not allowed

int a;

a = 8; // OK

static int a = 8; // OK

```

The Handel-C typeof operator allows you to determine the type of an object at compile time.

## 3.6.2 Handel-C v C: floating-point variables

There are no floating-point types (float, double or long double) in Handel-C.

Floating-point arithmetic is more complex than integer or fixed-point arithmetic and tends to require more hardware. If you are porting C code to Handel-C, check if there is a way to avoid using floating-points. For example, you might be able to use fixed-point values (which have a binary point), or to change the units to remove the decimal places (e.g. use pence or cents instead of pounds or dollars).

If you do need to use floating-point arithmetic, use the Celoxica floating-point library. This allows you to specify the exact width of the mantissa and exponent. You can download the floating-point library from the downloads section of the Celoxica support web site. If you can use fixed-point arithmetic, use the Celoxica fixed-point library. This is provided in the Platform Developer's Kit.

## 3.6.3 Handel-C v C: variable widths and casting

#### Handel-C widths

Handel-C types are not limited to specific widths. When you define a Handel-C variable, you should specify the minimum width required, to minimize hardware usage. For example, if you have a variable, x, that can hold a value between 1 and 20, use a 5-bit int:

```

int 5 x:

```

#### Casting

There is no automatic conversion between signed and unsigned values in Handel-C, you have to explicitly cast them:

```

int 12 x;

unsigned int 12 y;

y = x; //not allowed

y = (unsigned) x; //0K

```

Similarly, there is no automatic type conversion. If you wanted to add an int 5 and a long together, you would need to pad the int to 32 bits by using the concatenation operator. However, it would be more usual to perform arithmetic on ints of specific widths.

Pointers can be cast to void and back, to another pointer of the same type except for the addition or removal of a type qualifier, between signed and unsigned, and between similar structs (e.g. a struct with identical elements except for the width of the types).

You cannot perform the following casts in Handel-C:

- from a pointer of one type to a pointer of another type (except for those listed above)

- from a pointer to an integral type

- from an integral type to a pointer

- from a pointer to a function to a pointer to another function type

### Arithmetic and comparisons on variables of different width

In Handel-C you need to use the concatenation operator or the take operator when performing arithmetic or comparisons on variables of different width. For example:

```

int 12 x;

int 8 y;

x = y; \text{ // not allowed} y = x; \text{ //not allowed} x = y[7] @ y[7] @ y[7] @ y[7] @ y // 0K y = x <-8; \text{ // 0K; preserves the sign and copies the 7 LSBs}

```

Alternatively you can use the width adjustment macros in the Celoxica standard macro library, stdlib.hcl. The adju() macro adjusts the width of unsigned numbers and the adjs() macro adjusts the widths of signed numbers. The standard library is now provided as part of the Platform Developer's Kit (PDK). If you do not already have a copy of PDK, you can download it from the support section of the Celoxica web site.

#### sizeof

There is no sizeof in Handel-C. For simple types (signed and unsigned char, int, long and short), you can use the width operator. For example, sizeof long in C is equivalent to width long in Handel-C, except that the number of bytes is returned in C and the number of bits is returned in Handel-C.

#### 3.6.4 Handel-C v C: side effects

There are restrictions on how you can use side-effects in Handel-C, because each statement must only take one clock cycle. Each statement can only contain a single assignment, or an increment or a decrement.

This means that:

- Shortcut assignments (e.g. +=) must appear as standalone statements.

- The initialization and iteration phases of for loops must be statements, not expressions.

If you are porting ANSI-C code, complex statements have to be re-written as multiple single statements. It is often more efficient to run these statements in parallel. You cannot use comma operators in Handel-C.

If you had the following expression written in ANSI-C:

```

a = b = ++c, d+e;

```

this could be separated into single statements in Handel-C:

```

seq

{

++c;

b = d + e;

a = b;

}

```

However, you could rewrite the same code to run all the statements in parallel:

```

par

{

++c;

a = d + e;

b = d + e;

}

```

#### 3.6.5 Handel-C v C: functions

There are a number of differences in the way in which functions can be used in ANSI-C and Handel-C.

In Handel-C:

- Functions may not be called recursively, since all logic must be expanded at compile-time to generate hardware.

- You can only call functions in expression statements. These statements must not contain any other calls or assignments.

- Variable length parameter lists are not supported.

- Old-style ANSI-C function declarations (where the type of the parameters is not specified) are not supported.

- main() functions take no arguments and return no values.

- You can have more than one main() function. Each main() function is associated with a clock. If you have more than one main() function in the same source file, they must all use the same clock.

- You can have arrays of functions and inline functions. These are useful when you are writing parallel code.

### **Re-writing recursive functions**

If you want to port code that uses recursive functions to Handel-C, the options for rewriting it include:

- Using recursive macro expressions or recursive macro procedures. (It must be

possible to determine the depth of recursion at compile-time.)

- Creating multiple copies of a function.

• Re-writing the function to create iterative code. This is relatively easy if the function is calling itself (simple recursion), and the recursive call is the last item within the function definition (tail recursion).

The following ANSI-C function has simple tail recursion:

```

unsigned long Factorial (unsigned long n)

{

if (n==0)

return 1;

else

return n * Factorial (n-1);

}

It can be re-written in Handel-C as:

unsigned int 32 Factorial (unsigned int 32 n)

{

unsigned int 32 nfact;

nfact = 1;

if (n == 0)

delay;

else

{

while (n != 0)

{

nfact *= n;

--n;

}

}

return nfact;

```

Note that the if...else is required to prevent the possibility of a combinatorial loop if the while loop is not executed.

## 3.6.6 Handel-C v C: loop statements

for loops in Handel-C are slightly different to those in ANSI-C: the initialization and iteration steps are written as statements rather than expressions. This is because of restrictions on side effects in expressions in Handel-C.

You need to ensure that loop statements take at least one clock cycle in Handel-C. This means that:

• you cannot have empty loops in Handel-C

• you need to ensure that the body of a loop will always execute at least once, or else provide an alternative execution point using an if...else.

For example, if you had the following ANSI-C code:

```

while ((--i) != 0)

{

MyFunction (i);

}

```

The while loop would not be executed if i was equal to 0. You could re-write this in Handel-C as:

```

--i;

if (i != 0)

while (i != 0)

{

MyFunction (i);

--i;

}

else

delay;

```

Note that you need to decrement i before you enter the while body to preserve the order dependency of the ANSI-C code.

#### 3.6.7 Handel-C v C: unions

If there is no relationship between members of the union, you can use a struct instead.

If the members of the union are of related types (e.g. int, long and char), you can "reuse" a single variable which is the width of the widest variable in the union. For example, if you have the following union in your C code:

```

union

{

unsigned long ul;

unsigned char uc;

short ss;

} u:

```

you could use a single variable of the same width as the long:

```

unsigned int 32 i;

```

You could then get values equivalent to  $\mbox{ul}$ , ss and  $\mbox{ul}$  by casting and using the take operator:

u.ul would be written as i

u.uc would be written as i <-8

u.ss would be written as (signed) (i<-16)

Note that in ANSI-C there is no guarantee about whether ul, uc and ss would share storage, and so the Handel-C code above might not exactly reproduce the behaviour of the ANSI-C code in your C compiler.

### 3.6.8 Handel-C v C: data input and output

Handel-C does not have functions equivalent to <code>scanf()</code> and <code>printf()</code>. You can use <code>scanf()</code> and <code>printf()</code> when you are simulating a design, as Handel-C allows you to make calls to Handel-C functions. Alternatively, you can use the Handel-C <code>infile</code> and <code>outfile</code> specifications. Both these methods allow you to debug an algorithm before you build it in hardware.

When you are targeting hardware, data is passed between different parts of your Handel-C design using channels. If your Handel-C design will receive data from or send data to external components, you need to specify an interface. These external components might be written in EDIF, Verilog or VHDL, or they could be an additional component specified in Handel-C.

## 3.6.9 Handel-C v C: memory allocation

Memory allocation is not relevant when you are targeting hardware, so Handel-C has no equivalent of malloc and free.

You can use Handel-C to create RAM or ROM blocks on an FPGA or PLD, or interface to off-chip memory.

## 3.6.10 Handel-C v C: standard library

The standard library in Handel-C is called stdlib.hcl. This has no relationship to the C library, stdlib.lib or to stdio.lib.

stdlib.hcl contains bit manipulation and arithmetic macros.

The standard library is now provided as part of the Platform Developer's Kit (PDK). If you do not already have a copy of PDK, you can download it from the support section of the Celoxica web site.

## 3.6.11 C and Handel-C types and objects

| In both  | Conventional<br>C only | Handel-C<br>only |

|----------|------------------------|------------------|

| int      | double                 | chan             |

| unsigned | float                  | ram              |

| char     | union                  | rom              |

| long     |                        | wom              |

| short    |                        | mpram            |

| enum     |                        | signal           |

| register |                        | chanin           |

| static   |                        | chanout          |

| extern   |                        | undefined        |

| struct   |                        | interface        |

| volatile |                        | <>               |

| void     |                        | inline           |

| const    |                        | typeof           |

| auto     |                        |                  |

| signed   |                        |                  |

| typedef  |                        |                  |

# 3.6.12 Expressions in C and Handel-C

| In both                                   | Conventional<br>C only | Handel-C<br>only |

|-------------------------------------------|------------------------|------------------|

| <ul><li>* (pointer indirection)</li></ul> | sizeof                 | select()         |

| & (address of)                            |                        | width()          |

| -                                         |                        | @                |

| +                                         |                        | \\               |

| *                                         |                        | <-               |

| (multiplication)                          |                        |                  |

| /                                         |                        | [:]              |

|                                           |                        | let…in           |

| %                                         |                        |                  |

| <<                                        |                        |                  |

| >>                                        |                        |                  |

| >                                         |                        |                  |

| <                                         |                        |                  |

| >=                                        |                        |                  |

| <=                                        |                        |                  |

| ==                                        |                        |                  |

| !=                                        |                        |                  |

| & (bitwise and)                           |                        |                  |

| ۸                                         |                        |                  |

| 1                                         |                        |                  |

| ? :                                       |                        |                  |

| []                                        |                        |                  |

| !                                         |                        |                  |

| &&                                        |                        |                  |

| ~                                         |                        |                  |

| 11                                        |                        |                  |

| ->                                        |                        |                  |

#### 3.6.13 Statements in C and Handel-C

| In both    | Handel-C only                                                     |

|------------|-------------------------------------------------------------------|

| {;}        | par                                                               |

| switch     | delay                                                             |

| do … while | ?                                                                 |

| while      | !                                                                 |

| if … else  | prialt                                                            |

| for (;;)   | seq                                                               |

| break      | ifselect                                                          |

| continue   |                                                                   |

| return     |                                                                   |

| goto       |                                                                   |

| assert     | assert is an expression in Handel-C and not the same as in ANSI-C |

## 3.7 Handel-C constructs not found in ANSI-C

Handel-C is designed to target hardware. It allows you to specify timing and to target components such as memory, ports, buses and wires. One of the most important differences to ANSI-C is the ability to create code that executes in parallel.

Handel-C constructs that are not found in ANSI-C are listed below.

#### **Parallelism**

The par keyword specifies that a block of code should execute in parallel. Each statement within the block is executed in the same clock cycle. If the par keyword is not used, statements within a code block are executed sequentially. You can use the seq keyword to make this more explicit.

Channels allow communication between parallel branches of code. They are specified using the chan keyword, or by chanin and chanout when you are simulating code. You can read from and write to channels using statements of the form

```

Channel ? Variable; //reads from a channel Channel ! Expression; //writes to a channel

```

prialt statements are used with multiple channels, to select the first one that is ready for a read or write.

Semaphores (sema) allow you to coordinate the use of resources that are shared between parallel branches of code. The trysema() construct tests to see if the sema is owned.

The releasesema() construct frees a semaphore once it is no longer needed by a resource.

inline functions, arrays of functions, macro procedures and macro expressions help you to create multiple copies of functions. You need copies of a function if it is to be accessed by parallel branches of code.

### **Timing**

The set clock construct specifies the clock source for each main() function. You can have more than one clock interfacing with your design by specifying more than one main() function. If you want to simulate code, you can set a "dummy" clock. You can specify the frequency of a clock using the rate specification. The clockport specification can be used to assign a dedicated clock input resource on your target device. You can also use it to specify that a port on an interface is used to drive the Handel-C clock.

Assignments and delay take one clock cycle in Handel-C. Everything else is "free". The delay statement does nothing, but takes one clock cycle. This can be used to avoid timing conflicts, such as combinational loops.

The intime and outtime specifications can be used to specify the maximum delay between an interface and an element interacting with an interface, (e.g. the port reading data into a RAM).

### Compile-time selection and expansion and generic code

When you write code to target hardware, all logic needs to be expanded at compile time. This means that you cannot use recursive functions. However, macro procedures, macro expressions and shared expressions allow compile-time recursion in combination with the select, if select and let...in constructs.

The select operator allows you to select between expressions at compile time. It is similar to the conditional operator (cond ? expr1: expr2), but no hardware is generated for the conditional.

The ifselect construct is similar to an if...else, but selects between alternative blocks of code at compile time.

The typeof operator allows the type of an object to be determined at compile time. The undefined keyword specifies that the compiler should infer the width of a variable. These constructs allow you to create parameterizable code. For example, the Celoxica fixed-point library uses macros to pass the integer width and fraction width of a fixed-point number into code that creates a struct to hold the number.

#### Targeting hardware; FPGAs and PLDs

The set family and set part constructs allow you to specify the device you want to target in your source code. You can also set the device using the DK GUI.

### Targeting hardware; memory

The ram and rom keywords allow you to create on-chip RAM and ROM, and to interface to external RAM and ROM. If you want to create a block RAM, use the block specification.

To interface to off-chip RAMs or ROMs, use the offchip specification. The addr, data, we, cs, oe and clk specifications define the pins used between the FPGA/PLD and external RAM or ROM.

An mpram is a multi-ported RAM. This allows you to read from and write to a RAM within the same clock cycle, or to make two read or two write accesses. Individual ports can be specified as read/write, read-only and write-only using the ram, rom and wom keywords.

If you want to interface to a dedicated memory resource on the FPGA/PLD, use the ports specification.

The clkpulselen, rclkpos and wclkpos specifications allow you to synchronize a RAM clock with the Handel-C clock. The westart, welength and wegate specifications allow you to specify timing of a RAM clock that is asynchronous to the Handel-C clock.

### Targeting hardware; wires

If you specify a signal in Handel-C, this creates a wire in hardware. A signal takes on the value assigned to it but only for that clock cycle. The value assigned to it can be read back during the same clock cycle.

### Targeting hardware; resets

set reset allows you to reset your device into a known state. It can also be used to configure devices that are not in a known state at start up.

try...reset allows you to specify some actions that occur if a particular condition becomes true within a particular block of hardware.

#### Interfacing to existing modules and to peripherals

Handel-C interfaces can be used to connect to external devices or to external logic on your target FPGA/PLD, such as other programs written in Handel-C, VHDL or Verilog.

Port-type interfaces allow you connect to external logic. The bind, properties and std\_logic\_vector specifications allow you to parameterize interfaces connecting to external code.

Bus-type interfaces connect to pins connected to peripheral devices. The standard specification selects the I/O standard for interface pins and the strength specification determines the drive current. You can use the dci specification if you want to use digital controlled impedance. The pull specification allows you to create a pull up or pull down resistor for bus pins. The speed specification allows you to specify the slew rate for the output buffer on pins.

The extern "language" construct is the same as that found in C++. It allows you to connect to blocks of ANSI-C or C++ code for co-simulation.

#### Bit manipulation

Handel-C types are not constrained to a specific width, so you can specify the exact width needed for a variable to minimize hardware usage. Bit manipulation is required to connect objects of different widths. In addition to the ANSI-C bit manipulation operators,

Handel-C provides the take and drop operators, which take and drop the least significant bits of a variable, and the concatenation operator, to extend variable width. The bit selection operator, allows you to select individual bits of a variable.

# 4 Declarations

# 4.1 Introduction to types

Handel-C uses two kinds of objects: logic types and architecture types. The logic types specify variables. The architecture types specify variables that require a particular sort of hardware architecture (e.g., ROMs, RAMs and channels).

Both kinds are specified by their scope (static or extern), their size and their type. Architectural types are also specified by the logic type that uses them.

Both types can be used in derived types (such as structures, arrays or functions) but there may be some restrictions on the use of architectural types.

### **Specifiers**

The type specifiers signed, unsigned and undefined define whether the variable is signed and whether it takes a default defined width.

You can use the storage class specifiers extern and static to define the scope of any variable.

Functions can have the storage class inline to show that they are expanded in line, rather than being shared.

#### Type qualifiers

Handel-C supports the type qualifiers const and volatile to increase compatibility with ANSI-C. These can be used to further qualify logic types.

#### Disambiguator

Handel-C supports the extension < >. This can be used to clarify complex declarations of architectural types.

### 4.1.1 Handel-C values and widths

A crucial difference between Handel-C and conventional C is Handel-C's ability to handle values of arbitrary width. Since conventional C is targeted at general-purpose microprocessors it handles 8, 16 and 32 bit values well but cannot easily handle other widths. When targeting hardware, there is no reason to be tied to these data widths and so Handel-C has been extended to allow types of any number of bits.

Handel-C has also been extended to cope with extracting bits from values and joining values together to form wider values. These operations require no hardware and can provide great performance improvements over software.

When writing programs in Handel-C, care should be taken that data paths are no wider than necessary to minimize hardware usage. While it may be valid to use 32-bit values for all items, a large amount of unnecessary hardware is produced if none of these values exceed 4 bits.

Care must also be taken that values do not overflow their width. This is more of an issue with Handel-C than with conventional C because variables should be just wide enough to contain the largest value required (and no wider).

You cannot cast a variable or expression to a type with a different width. Use the concatenation operator to zero pad or sign extend a variable to a given width.

## 4.1.2 String constants

String constants are allowed in Handel-C. A string constant consists of a string of characters delimited by double quotes ("). They will be stored as a null-terminated array of characters (as in ANSI-C). String constants can contain any of the special characters listed below. Arrays and pointers can be initialized with string constants, and string constants can be assigned to pointers. If a string constant is assigned to a pointer, the storage for the string will be created implicitly.

### Special characters:

alert

\a

| \b  | backspace       |

|-----|-----------------|

| \f  | formfeed        |

| \n  | newline         |

| \r  | carriage return |

| \t  | tab             |

| \ V | vertical tab    |

| \\  | backslash       |

| \?  | question mark   |

| \'  | single quote    |

\onumber octal number e.g. \o77

double quote

\x*number* hexadecimal number e.g. \xf3

#### 4.1.3 Constants

Constants may be used in expressions. Decimal constants are written as simply the number while hexadecimal constants must be prefixed with 0x or 0X, octal constants

must be prefixed with a zero and binary constants must be prefixed with 0b or 0B. For example:

```

w = 1234;  /* Decimal */

x = 0x1234;  /* Hexadecimal */

y = 01234;  /* Octal */

z = 0b00100110;  /* Binary */

```

The width of a constant may be explicitly given by 'casting'. For example:

```

x = (unsigned int 3) 1;

```

Casting may be necessary where the compiler is unable to infer the width of the constant from its usage.

# 4.2 Logic types

The basic logic type is an int. It may be qualified as signed or unsigned. Integers can be manually assigned a width by the programmer or the compiler will attempt to infer a width from use.

Enumeration types (enums) allow you to define a specified set of values that a variable of this type may hold.

There are derived types (types that are derived from the basic types). These are arrays, pointers, structs bit fields, and functions. The non-type void enables you to declare empty parameter lists or functions that do not return a value. The typeof type operator allows you to reference the type of a variable.

#### 4.2.1 int

There is only one fundamental type for variables: int. By default, integers are signed. The int type may be qualified with the unsigned keyword to indicate that the variable only contains positive integers or 0. For example:

```

int 5 x;

unsigned int 13 y;

```

These two lines declare two variables: a 5-bit signed integer x and a 13-bit non-negative integer y. In the second example here, the int keyword is optional. Thus, the following two declarations are equivalent.

```

unsigned int 6 x;

unsigned 6 x;

```

You may use the signed keyword to make it clear that the default type is used. The following declarations are equivalent.

```

int 5 x;

signed int 5 x;

signed 5 x;

```

The range of an 8-bit signed integer is -128 to 127 while the range of an 8-bit unsigned integer is 0 to 255 inclusive. This is because signed integers use 2's complement representation.

You may declare a number of variables of the same type and width simultaneously. For example:

```

int 17 x, y, z;

```

This declares three 17-bit wide signed integers x, y and z.

# 4.2.2 Signed | unsigned syntax

Signed | unsigned is declared in the same way as in ANSI-C except that Handel-C allows the width to be declared. The width may be undefined, an expression, or nothing.

For example:

- int a;

- long b;

- unsigned int 7 c;

- signed undefined d;

- long signed int e;

## 4.2.3 Supported types for porting

Handel-C provides support for porting from conventional C by allowing the types char, short and long. For example:

```

unsigned char w;

short y;

unsigned long z;

```

Note that these are fixed-widths in Handel-C, and implementation dependent in ANSI-C. The widths used for each of these types in Handel-C is as follows:

Type Width

char 8 bits (signed)

short 16 bits long 32 bits

Smaller and more efficient hardware will be produced by using variables of the smallest possible width.

# 4.2.4 Inferring widths

The Handel-C compiler can infer the width of variables from their usage. It is therefore not always necessary to explicitly define the width of all variables and the undefined keyword can be used to tell the compiler to try to infer the width of a variable. For example:

```

int 6 x;

int undefined y;

x = y;

```

In this example the variable x has been declared to be 6 bits wide and the variable y has been declared with no explicit width. The compiler can infer that y must be 6 bits wide from the assignment operation later in the program and sets the width of y to this value.

If the compiler cannot infer all the undefined widths, it will generate errors detailing which widths it could not infer.

The undefined keyword is optional, so the two definitions below are equivalent:

```

int x;

int undefined x;

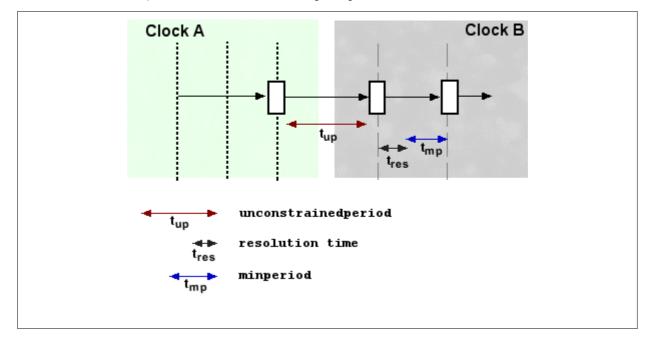

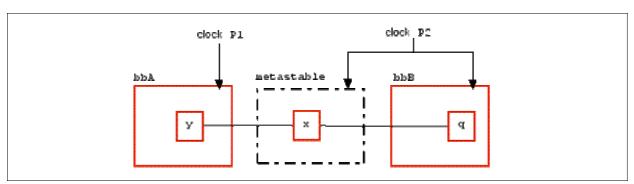

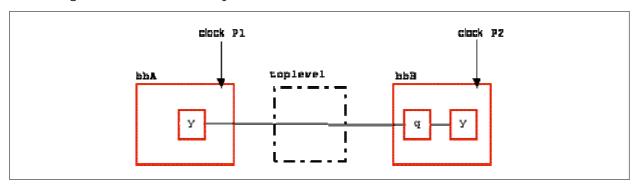

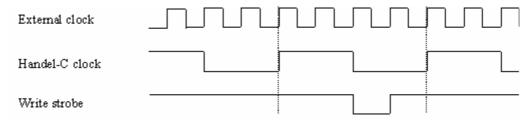

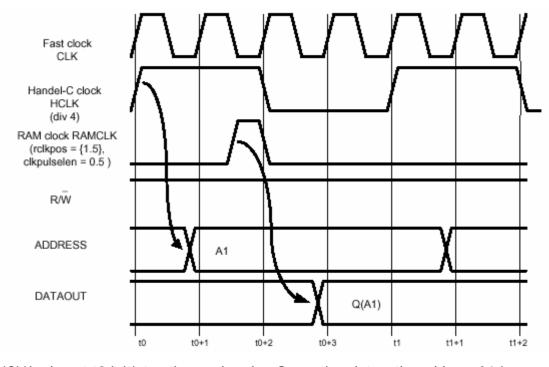

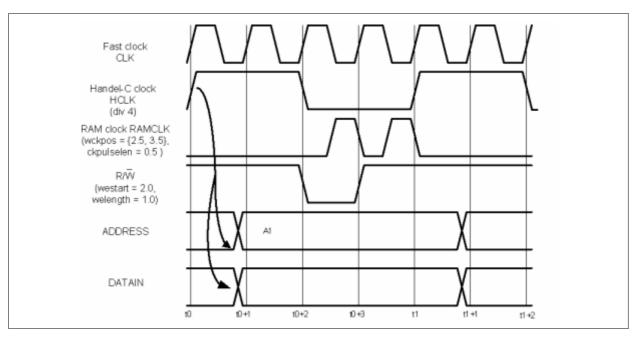

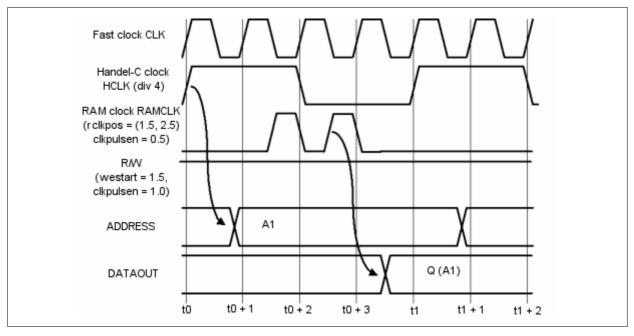

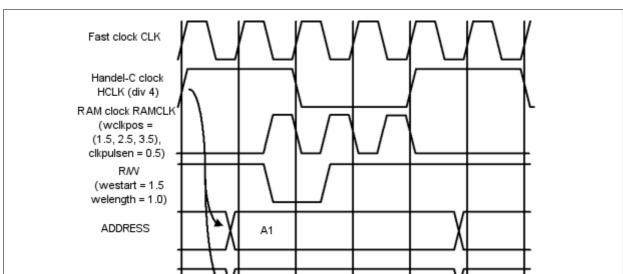

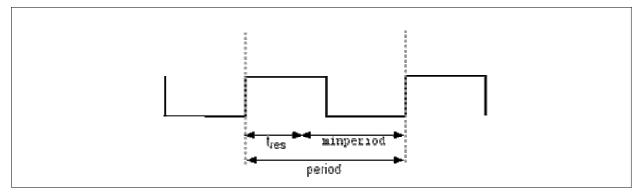

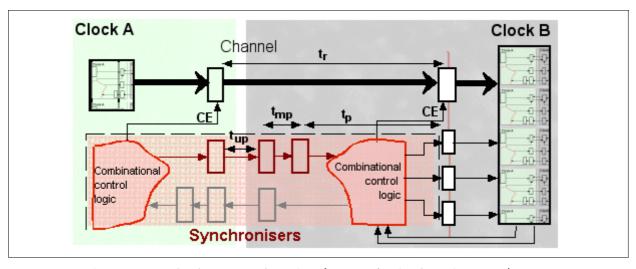

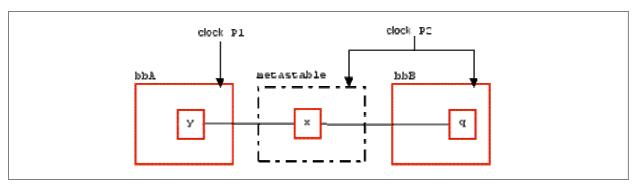

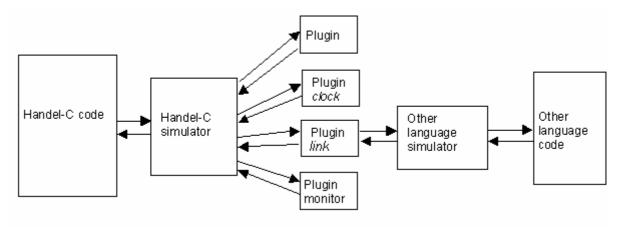

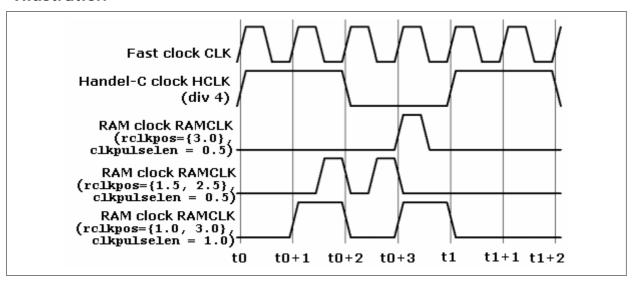

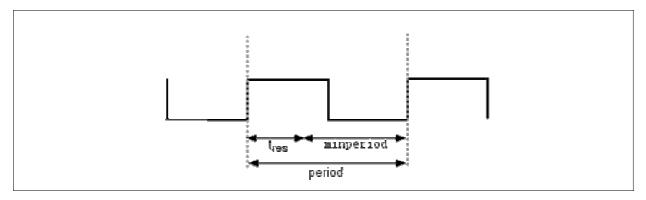

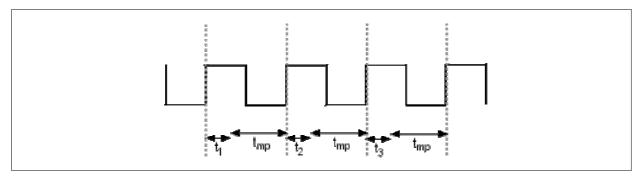

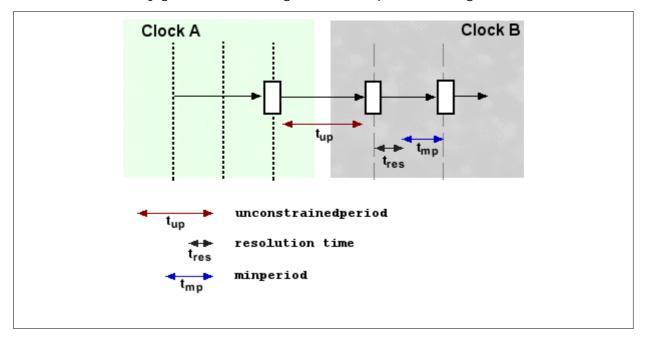

```